|

|

|

|

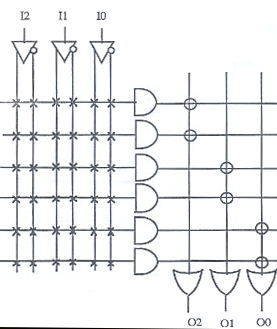

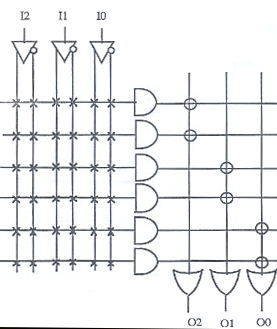

Fonctions logiques ŕ diodes:

Structure ET et Structure OU et association des deux structures pour

matérialiser des équations logiques telles qu'elles peuvent ętre

issues d'un tableau de Karnaugh |

En 1975

Signetics sort le premier circuit logique programmable.

Depuis sa création en 1961, par 4 ingénieurs, émanation de Fairchild, la

société signetics qui s'était spécialisée dans les circuits intégrés ŕ la

demande mais qui se voyait de plus en plus en difficulté fut sauvée par l'armée

américaine. Cette derničre récemment convaincue de l'importance d'utiliser des

circuits intégrés dans ses systčmes afin de réduire: poids, encombrement et

consommation s'orienta vers Signetics en 1963 qui pouvait répondre ŕ sa demande

de circuits spéciaux . Des 1964 les commandes militaires améliorčrent la caisse

et la réputation.

En 1975 Signetics commercialise le premier circuit de logiques programmable , le

FPLA (Field Programmable Logic Array ) 82S100. Le schéma interne est voisin des fonctions représentées ci dessus les

variables d'entrées (ci dessus A et B, ) sont au nombre de 16. Ces 16 entrées et

leur inverse vont pouvoir

ętre dirigées vers 48 fonctions ET de 1 ŕ 16 entrées, ces 48 portes

ET convergent

vers 8 OU qui vont constituer les sorties. Chaque entrée et son inverse est

reliées aux 48 ET par des fusibles en Ni-Cr qui seront

ou maintenus ou claqués par le programmateur , chaque sortie ET est envoyée vers

les entrées des 8 OU par l'intermédiaire de fusibles qui seront

maintenus ou claqués ŕ la programmation.

La premičre matrice de connexion comportait donc

32 lignes

horizontales

qui se croisaient avec

768 lignes verticales

, ŕ chaque intersection un fusible de NiC ( 24 576) et les 48

sorties ET se croisaient avec les 8 fois 48 entrées des portes OU

soit 18 432 fusibles.

Quelques caractéristiques du 82S100

|

|

|

|

Le FPLA 82S100 de Signetics |

La

technologie employée par Signetics ( RTC - Philips...)

utilise des diodes schotky pour réaliser les portes ET et

des transistors montés en émetteur suiveur pour les portes

OU |

En 1978 MMI (Monolithic

Memories) introduit le PAL

Ce sont des circuits programmables dans lesquels seules les portes

ET peuvent ętre connectées aux entrées ou ŕ leur complément . En

fait, comme le FPLA les portes ET ŕ l'état vierge sont connectées ŕ

toutes les entrées et leur complément , la programmation consiste ŕ

éliminer les connexions inutiles en claquant les fusibles qui

assurent cette connexion. Les portes OU connectées aux sorties ne

sont pas programmables . Ces circuits plus simples que les

précédents sont sensés ętre plus rapides et notamment moins chers

Les PAL se complexifient avec le temps et notamment par l'introduction

de registres qui vont permettre de mémoriser des sorties pour les

réinjecter sur les entrées et ainsi en faire une " machine d'états"

c'est ŕ dire que le circuit n'est plus simplement combinatoire, il

devient séquentiel . Les sorties ne sont plus simplement une combinaison

des variables d'entrées mais aussi dépendantes de l'état antérieur du

circuit. L'introduction de registres sur les entrées permet un

synchronisme de l'apparition des variables et évite des fluctuations du

circuit

Les

FPGA sont plus évolués que les circuits précédents , ils sont

composés de cellules dont la taille est trčs différente d'un fabriquant

ŕ l'autre. La granulométrie est un indicateur de la taille des

cellules. La granulométrie va de la plus fine chez Actel ŕ la plus

grosse chez Xilinx ou Altera . Chaque option a ses avantages et ses

inconvénients. Une granulométrie fine suppose une meilleure utilisation

de l'ensemble des cellules du circuit mais une place importante utilisée

pour les interconnexions . Une grosse granulométrie peut mener ŕ

utiliser une cellule trčs importante pour faire une simple porte ET

|

cellules et interconnexion

des cellules |

|

|

|

|

|

|

|

ACTEL

Technologie antifusible. Aucune connexion n'est faite ŕ l'état

vierge. La connexion sont réalisées par mise en court-circuit

des antifusibles.

Avantage: pas de métal diffusé dans l'environnement de la

puce pouvant se déposer de façon aléatoire. Processus sűr

notamment pour du matériel aéronautique notamment .

Inconvénient: programmable une seule fois

point 2016 on relčve un circuit comportant 146 124

cellules avec 574 E/S |

XILINX (maintenant INTEL)

Le programme est

contenu dans un circuit annexe et se transfčre ŕ la mise

sous tension, technologie des RAMs statiques

Avantage: le circuit est reprogrammable ŕ l'infini.

Particuličrement appréciable lors de la mise au point d'un

montage.

Inconvénient: Systčme ŕ la merci de perturbations

électromagnétiques lors du transfert de la configuration du

circuit ŕ chaque mise sous tension

point 2016 on relčve un circuit comportant 3 578 cellules

avec 832 E/S |

ALTERA

Technologie EPROM

point 2016 on relčve un circuit comportant 5 510 000

cellules avec 1 640 E/S |