Si vous souhaitez des renseignements

techniques plus substantiels, vous pourrez les trouver, à l'exception de la

technologie RTL,

sur ce site dans le cours sur la

technologie des circuits intégrés

|

Inventés par Kilby et

Noyce ,(voir la fiche

précédente) les circuits intégrés ont vu le

jour en 1958. Concernés essentiellement par les origines de l'informatique, nous

nous intéresserons principalement aux circuit logiques

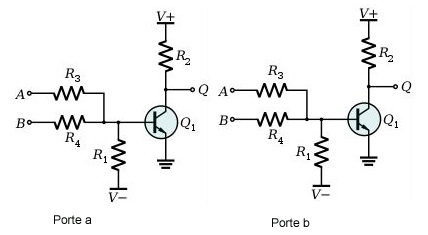

TECHNOLOGIE RTL

Nous voyons que ce type de porte va être très sensible au calibrage des potentiels appliqués sur les entrées, d'autre part elle nécessite une alimentation +V et -V. Cette technologie sera vite abandonnée TECHNOLOGIE DTL (

voir

le cours DTL et TTL)

|

|||||||||||||||||||||||||||||||||||

|

La porte DTL ci dessus est simple et fonctionne bien. Cependant

elle ne commute pas très rapidement. Pour en comprendre la raison il faut faire

apparaître notamment, les capacité parasites. Pour qu'une diode passe de l'état

passant à l'état bloqué, il est nécessaire de favoriser les chemins pour

l'écoulement des charges contenues dans la jonction, de même une diode à l'état

bloqué se comporte comme un condensateur qui doit se charger.

TECHNOLOGIE TTL avec sortie dite Totem pole ( voir le cours DTL et TTL)

TECHNOLOGIE TTL Schottky ( voir le cours DTL et TTL) Lorsqu'un transistor est sur saturé, le potentiel de la base est plus élevé que celui du collecteur, et le transistor est long à se bloquer. Si nous plaçons une diode shottky dont la tension de déchet est de l'ordre de 0,4volt entre base et collecteur, le potentiel du collecteur ne pourra pas descendre en dessous de (Vb-0,4V). Il s'en suit une adaptation de la saturation du transistor à la charge et donc une amélioration de la rapidité de blocage.

Le besoin de vitesse dans les circuits logiques s'oriente vers des circuits logiques dont les transistors bipolaires ne sont jamais saturés , ce sont les logiques à couplage d'émetteurs ECL TECHNOLOGIE ECL (voir le cours ECL)

TECHNOLOGIE CMOS (voir le cours MOS-CMOS) L'emploi de transistor Mos complémentaires, c'est à dire des Mos canal N et canal P, à enrichissement sur la même puce. Permet une extrême simplification des portes logiques. Un Mos à enrichissement est bloqué en l'absence de commande. Un transistor canal P est passant lorsque Vgs est négatif pour Vgs = 0 il est bloqué pour le canal N si Vgs est positif il est passant pour Vgs= 0 il est bloqué. Un transistor Mos à enrichissement bloqué se comporte comme une résistance de plusieurs MΏ, à l'état passant c'est une résistance de quelques dizaines d'ohms. Si une porte CMOS alimente une entrée capacitive, ce qui est le cas pour une entrée de porte CMOS , la fourniture d'un état logique après quelques constantes de temps , cet état logique courrespond exactement aux tensions d'alimentation des circuits, ce qui donne une bonne immunité au bruit.

| |||||||||||||||||||||||||||||||||||

|

|||||||||||||||||||||||||||||||||||